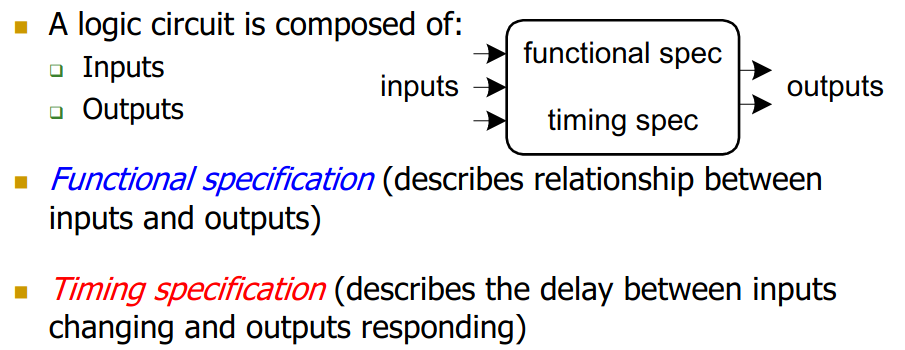

Now that we understand basic logic gate structure, we can combine them to build more complex structures.

To do so, we will build a framework for specifying our circuit.

We will first approach combination logic, which is memoryless, i.e. the ouputs are strictly dependent on the combination of input values being applied right now.

2.1 Boolean Algebra - Foundation of Logic Design

2.2.1 Basic Operations

There are three fundamental operations in boolean algebra.

Operations Boolean Algebra

- Not / Complement

- AND

- OR

Boolean algebra is:

- closed with regards to those operations.

- commutative

- each have an identity (0 for OR and 1 for AND)

- distributive law holds

- Complement

- OR on the complement gives AND neutral

- AND on the complement gives OR neutral

2.1.2 Duality

By swapping AND with OR, 0s with 1s but not any literals or anything else, we still get a valid boolean equation.

Example:

- is equivalent to which is the dual of De Morgan’s law.

2.1.3 Useful Laws

Boolean Algebra, Useful Laws

- Operations with and :

- (dual of the previous)

- Idempotent Law

- Involution Law

- Law of Complementarity

- and

- Commutativity

- Associativity

- Distributivity

Simplification Theorems

Useful to remember!

- and it’s dual

- and

- and

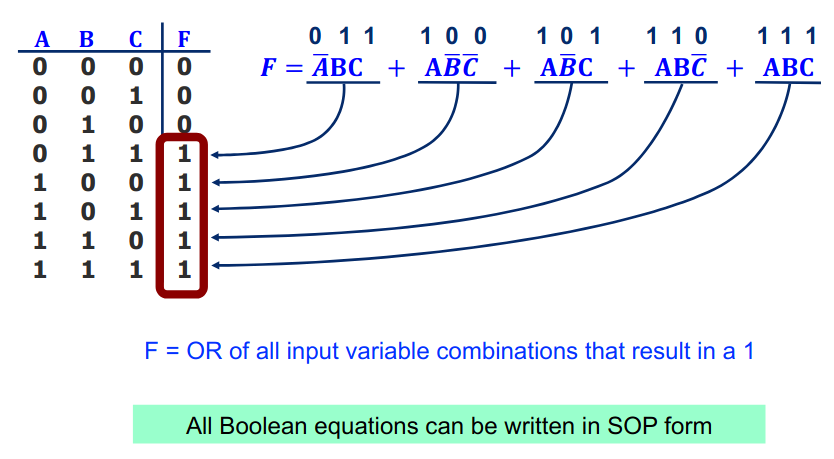

2.1.4 Standardised Function Representations

Using canonical representations (SOP and POS, equivalent to DNF and CNF), we can communicate a components operation exactly, which allows computer aided design or automation.

One function can have many hardware representations, but we standardise it’s form using SOP or POS.

The standard forms:

- Sum of Products (DNF)

- Product of Sums (CNF)

Some vocabulary:

- Implicant: product term that implies the function (i.e. if the product term is , the function is ). Can be single literal or combination ANDed together.

- Minterm: product term (AND term) that includes all input variables (either in true or complement form). A Minterm is for exactly row of the truth table.

- Maxterm: sum term (OR term) that includes all input variables. (Is for exactly one row).

The SOP form of some function given as a set of minterms.

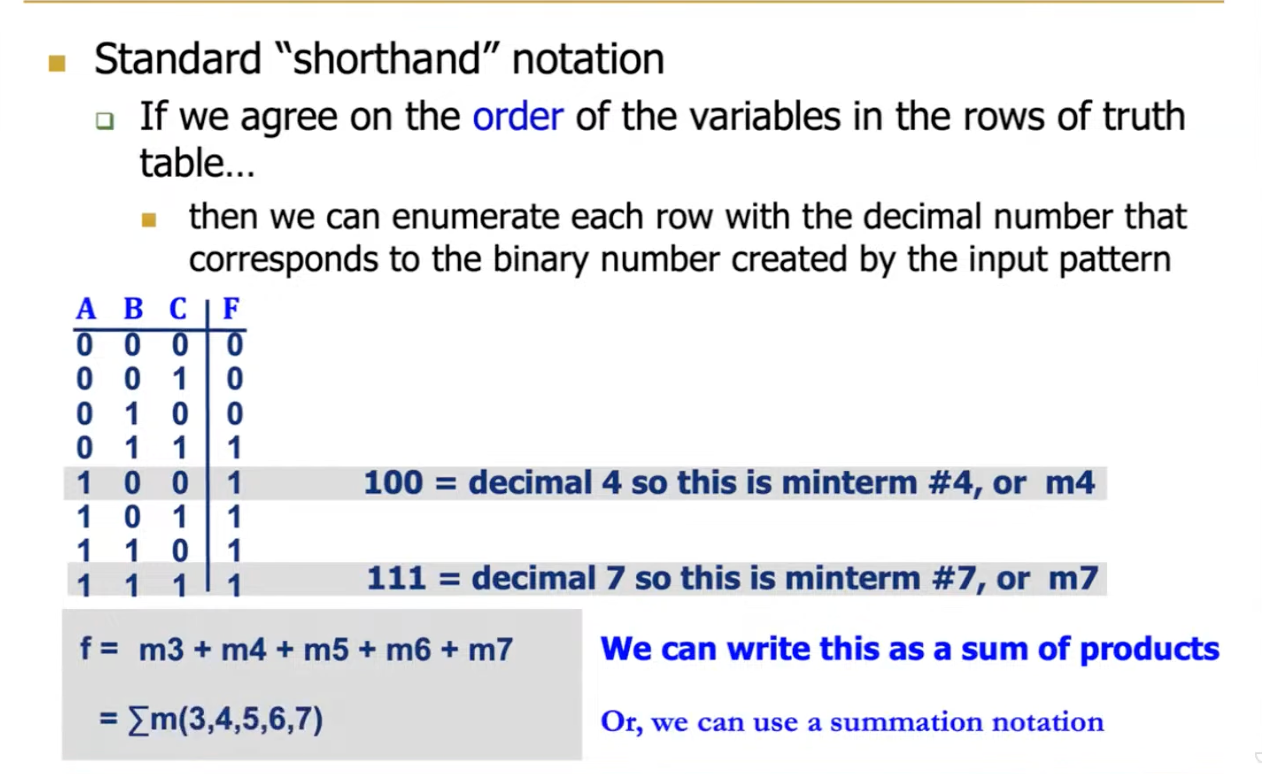

2.1.5 Sigma Notation (Standard)

The boolean table is a unique signature of our function, but it is expensive. We can give the SOP or POS form as a standardised way to communicate the function table more efficiently.

We can then use logic minimisation techniques to automate it’s actual implementation in hardware.

We can then give the function in either SOP form

or POS form

which are “complementing” each other as is clear. There are some useful rewriting rules.

- Minterm to Maxterm / Maxterm to Minterm

- Rewrite the shorthand to use Maxterm and replace indices by those not already used (see above)

- Expansion of to expansion of

- gives us

- gives us

- “invert” the indices

- Minterm of to Maxterm of *

- gives us

- gives us

- Use same indices but go from max- to minterm

2.2 Basic Combinational Blocks

There are foundational building blocks of logic which enables reuse in order to facilitate building more complex systems: Decoder, Multiplexer, Full Adder, PLA, etc…

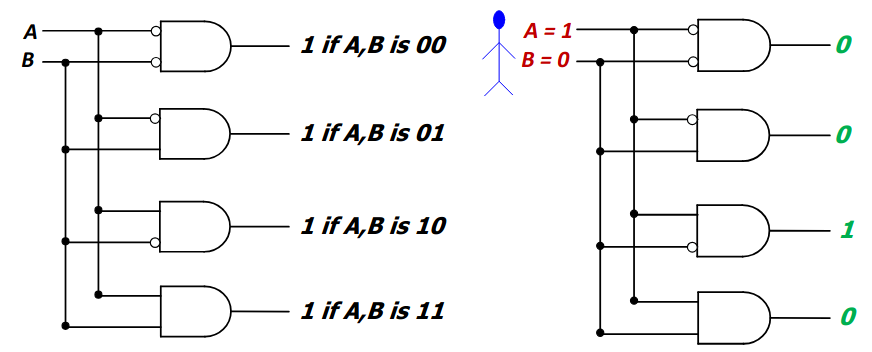

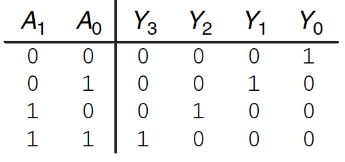

2.2.1 Decoder

Inputs n Outputs

The decoder is basically a “pattern detector”.

Such a decoder is useful in memory address finding or decoding the instruction in the ALU.

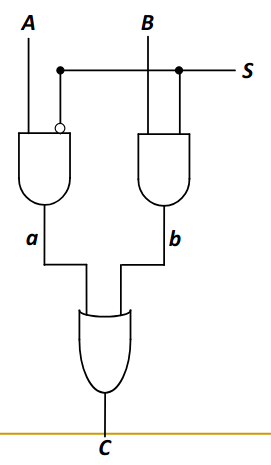

2.2.2 Multiplexer

Input n Output

Selects one of the inputs to connect to the output, based on the select signal.

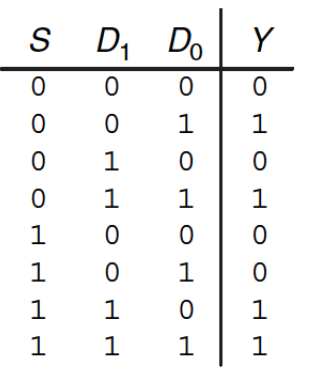

We can use multiplexers as “lookup” tables to perform logic functions for example. The following is an example of a 3 LUT.

LUT

-LUT can implement any -bit input function.

Note, we could use a decoder in the same way, by ORing between the outputs for which we want it to evaluate to (see slide 103 in the second lecture).

2.2.3 Full Adder

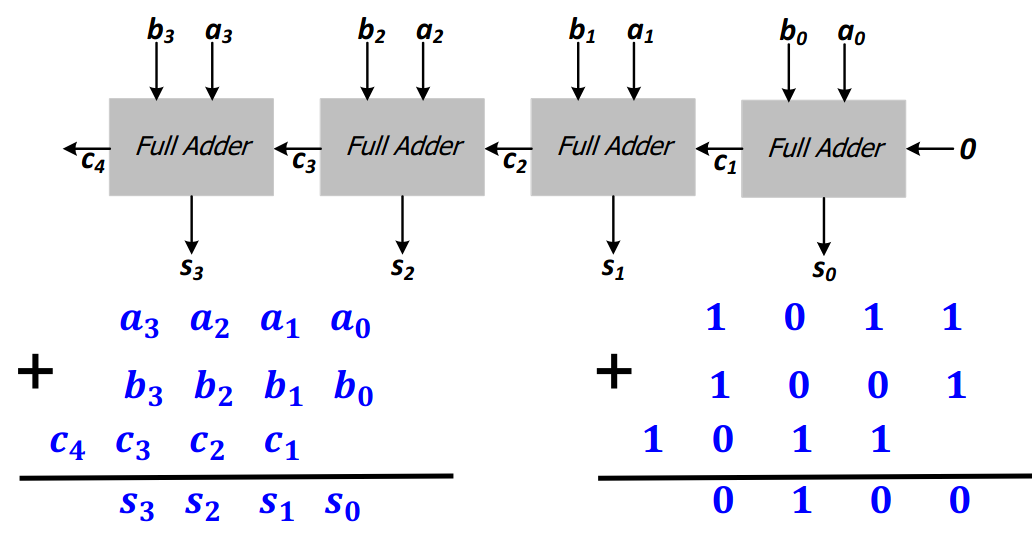

The full adder carries out binary addition with a carry bit.

Example: so adding with the carry bit set gives us and is carried, in binary so this indeed works out.

We can chain the adders in order to add multiple bits, by daisy-chaining the carry bits. This is called a ripple carry adder.

This does have the problem of latency, which is why we would use more optimised circuitry for longer additions.

We can instead use specialised logic for fast carry calculation and perform addition in parallel.

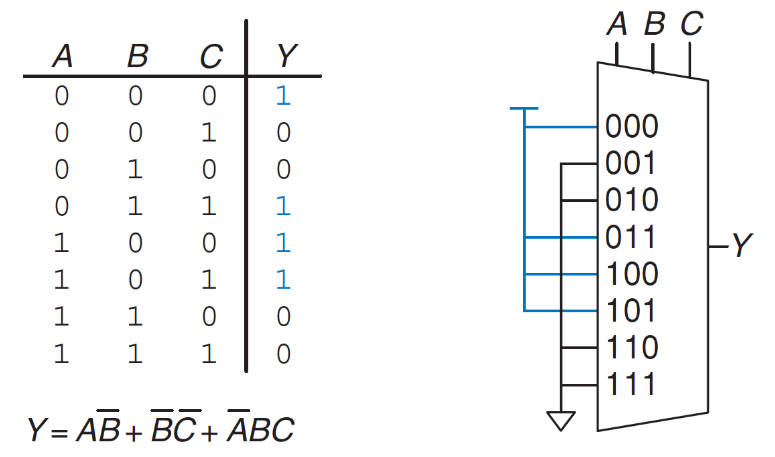

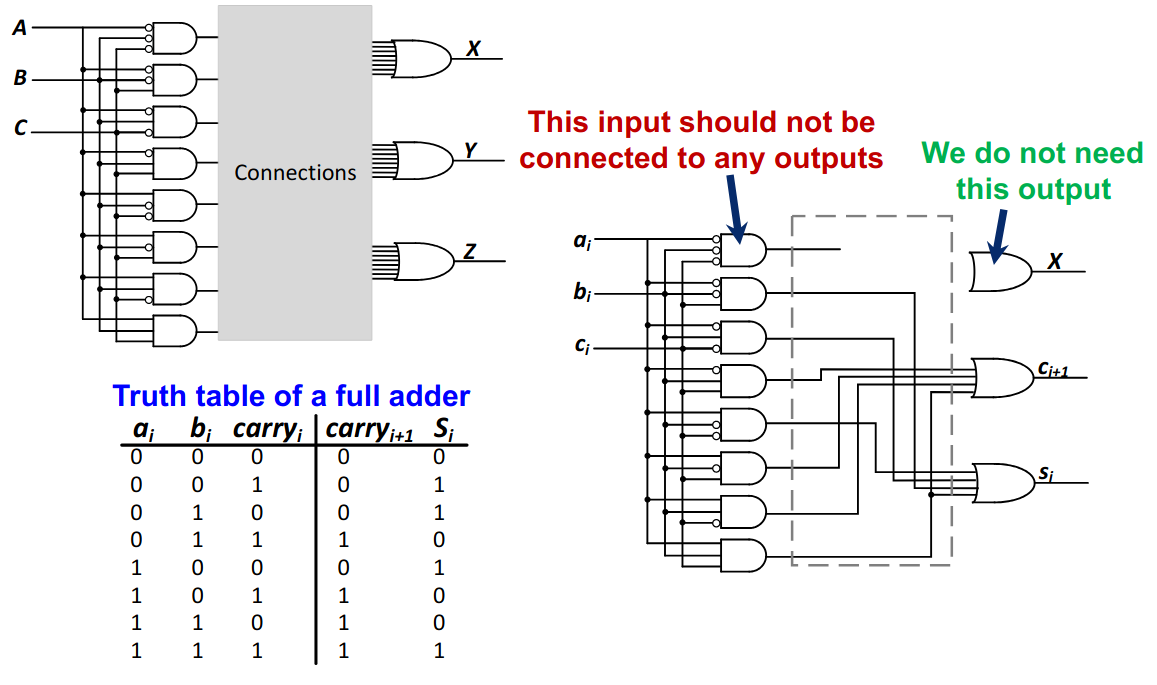

2.2.4 Programmable Logic Array (PLA)

By using a PLA, we can simply the design/implementation of a function in hardware.

We use a column of ANDs (negating as needed) and connect them to ORs as output. This is exactly SOP form implemented.

We can implement a full adder as a PLA, as seen here:

We wire up the implicants to the OR gates and get the outputs.

2.2.5 Comparator

Checks if two -input values are exactly the same by wiring each pair of inputs into an XNOR gate and summing up with an AND.

2.2.6 Arithmetic Logic Unit (ALU)

The ALU takes a “word” as an input which decides which operation to perform on inputs (as defined in the instruction set).

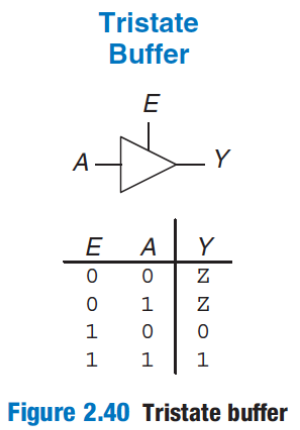

2.2.7 Tri-State Buffer

Enable gating of different signals onto a wire.

While the E is low, the output stays the same as before, once we set E high, it is updated from the input.

For example, when we have a gate between CPU and memory, we want to only allow one device to write to it at the same time.

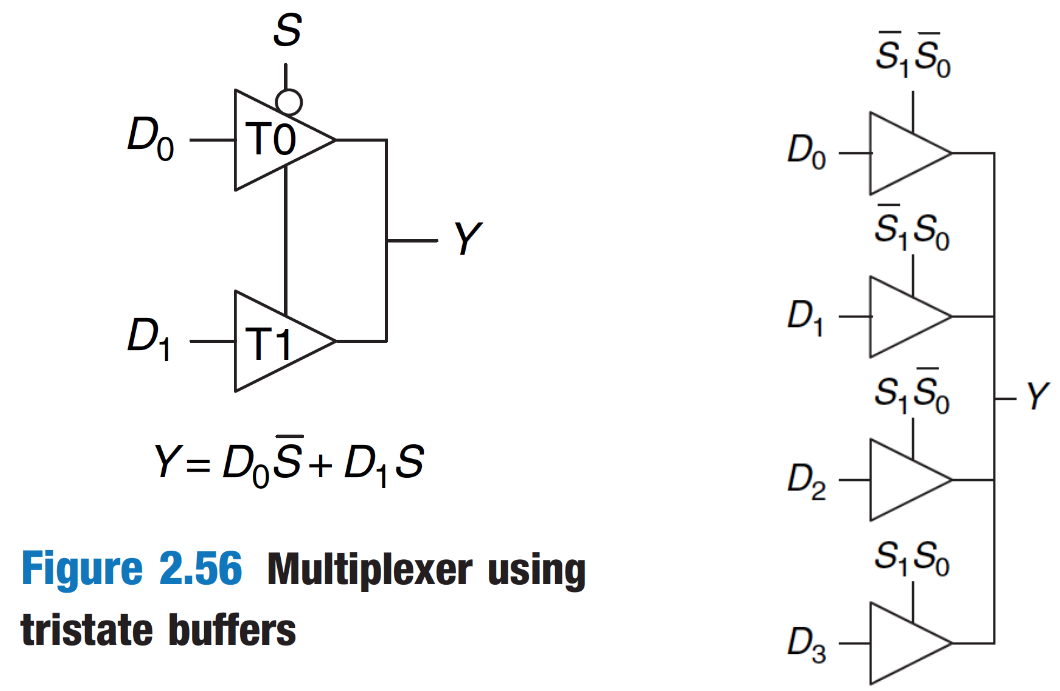

We can also build a multiplexer in this way, by configuring the enable in such a way that it enable the correct input for each combination:

2.3 Logical (Functional Completeness)

We can implement any logic function we wish with a PLA, which consists only of AND, OR and inverters. This is because the set of gates {AND, OR, NOT} is logically complete.

Any function can be rewritten in SOP or POS form.

NAND is also logically complete, as we can easily show by expressing {AND, OR, NOT} in terms of only NAND gates.

2.4 Simplifying

Even though we can use SOP to implement any logic function in a PLA, this is often inefficient. We can use way less gates.

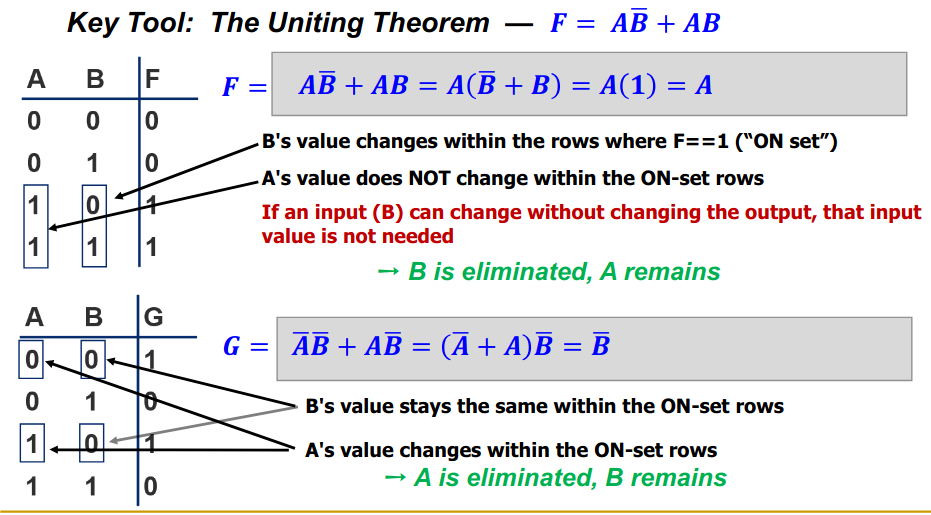

2.4.1 Uniting Theorem

If two product terms differ only in one variable (variable and it’s complement), the variable can be eliminated:

We identify pairs of min-terms from which we can eliminate variables.

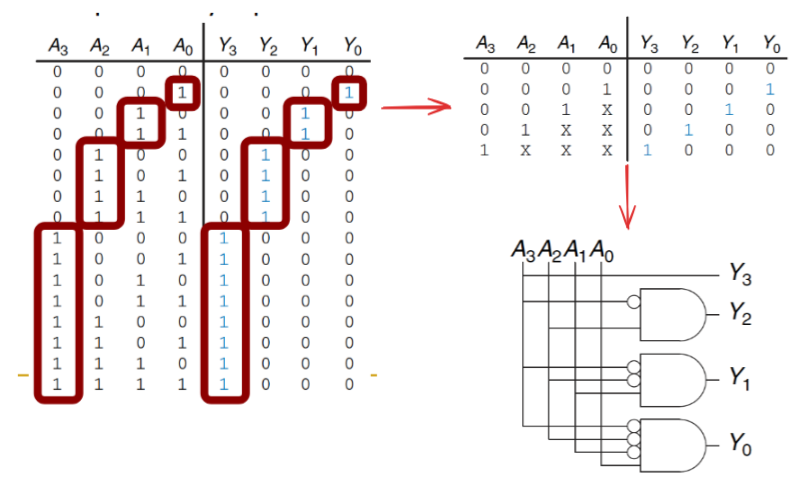

2.4.2 Don’t Cares

By implementing “don’t cares” as in the truth table, we can reduce complexity by a lot. We go from a giant truth table to a 4 row one.

This is essentially the uniting theorem in “graphical version”. We group a number of min-terms together while building the function table, essentially eliminating variables.